近年来,随着人工智能技术的快速发展和应用场景的不断扩展,人工智能芯片市场需求快速增长。大模型时代的到来对人工智能芯片提出更高要求,尤其是在提升算力、降低功耗、提高能效方面。2.5d/3d封装、存算一体、类脑芯片是高算力、高能效人工智能芯片的重要发展方向。近期,国新基金邀请北京大学集成电路学院博雅特聘教授叶乐围绕“人工智能芯片行业发展与投资机遇”进行了专题分享。本文结合分享内容对人工智能芯片行业发展现状及趋势进行分析,供参考。

一、人工智能芯片定义及分类

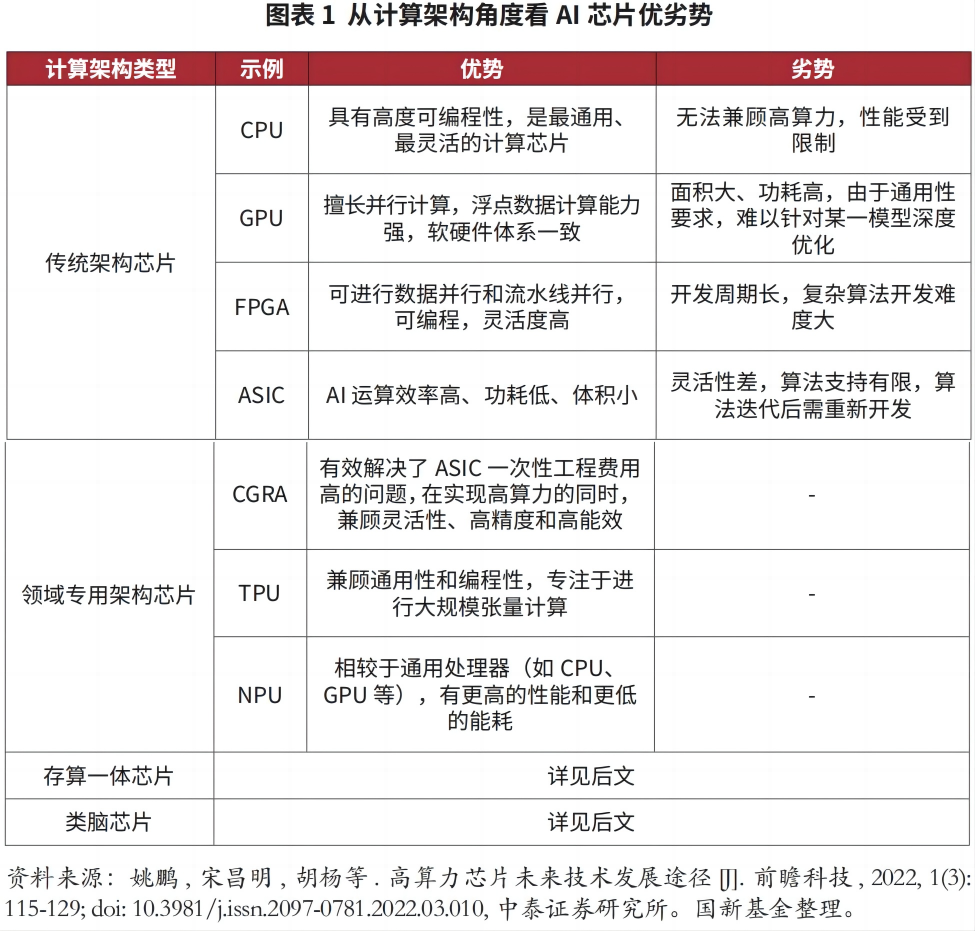

人工智能芯片(ai芯片)指针对人工智能算法进行特殊加速设计的芯片。从应用场景角度,ai芯片可分为云端的训练芯片、推理芯片,以及边缘端的推理芯片。从计算架构角度,ai芯片可分为传统架构芯片、领域专用架构芯片、存算一体芯片、类脑芯片等,各自优劣势如图表1所示。

二、大模型对人工智能芯片的深远影响

2012年以来人工智能算法突飞猛进,复杂度不断提高,底层硬件的发展难以满足算法需求,芯片适配问题迫在眉睫,通用性强成为选择芯片时的首要考虑因素。gpu凭借其并行运算能力强于cpu,且cuda生态可实现通用化,一直是人工智能领域的主流算力芯片。大模型的出现和快速发展对ai芯片产生深远影响,对ai芯片日益多元化(低功耗、高带宽)的需求使gpu之外的技术路线有了弯道超车的机会。

具体而言,一是人工智能算法框架已经开始收敛至transformer算子〔1〕,算子中90%均为矩阵运算,对芯片通用性的要求有所降低,放弃一定的通用性而专门针对大模型进行加速成为可能。二是gpu的较高成本导致当前大模型尚未形成商业闭环。由于gpu功耗高、能效差,以gpu为主导的数据中心仅30%的成本是硬件投入,60%的成本都来自于芯片本身工作和散热所产生的电费。为解决此痛点,未来ai芯片在支持主流算法的前提下,更重要的目标是提升算力、降低功耗,从而提高整体能效,为下游客户降低成本。

三、高算力和低功耗ai芯片的典型技术路线

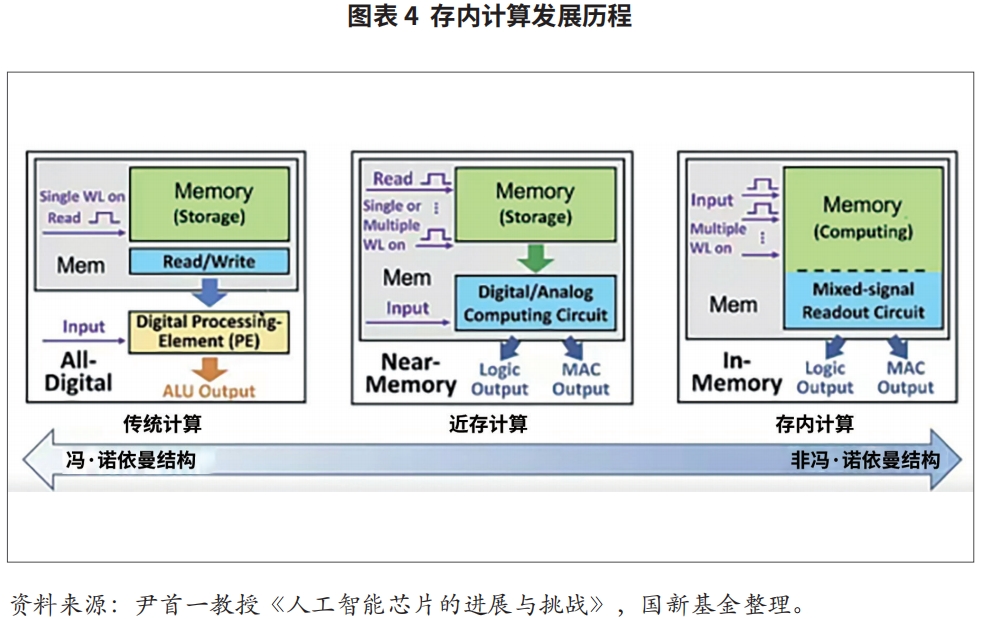

在传统的冯·诺依曼架构中,存储单元和计算单元彼此分离,虽然可编程性高、通用性强,但任务处理需要数据频繁地在存储单元和计算单元之间搬移,搬移过程中的延时和功耗成为系统性能瓶颈,导致“存储墙”和“功耗墙”,制约芯片算力的进一步提升。为解决上述问题,目前主要有以下三种典型的技术路线,可以互相结合使用。

(一)2.5d/3d封装

后摩尔时代,芯粒(chiplet)技术成为学术界和产业界普遍看好的关键突破方向之一。通过将芯片中不同功能设计模块切割划分为多颗芯粒,各自采用最适合的工艺节点生产,而无需统一采用先进制程,可有效降低流片开销。各颗芯粒面积较小,也有利于良率提升,进一步降低成本。芯粒技术的核心是封装、互连技术以及全新的系统设计方法学,采用高密度、高速的封装和互连设计,还可以提升计算和存储、计算和计算之间的通信带宽,进一步提升芯片算力〔2〕。

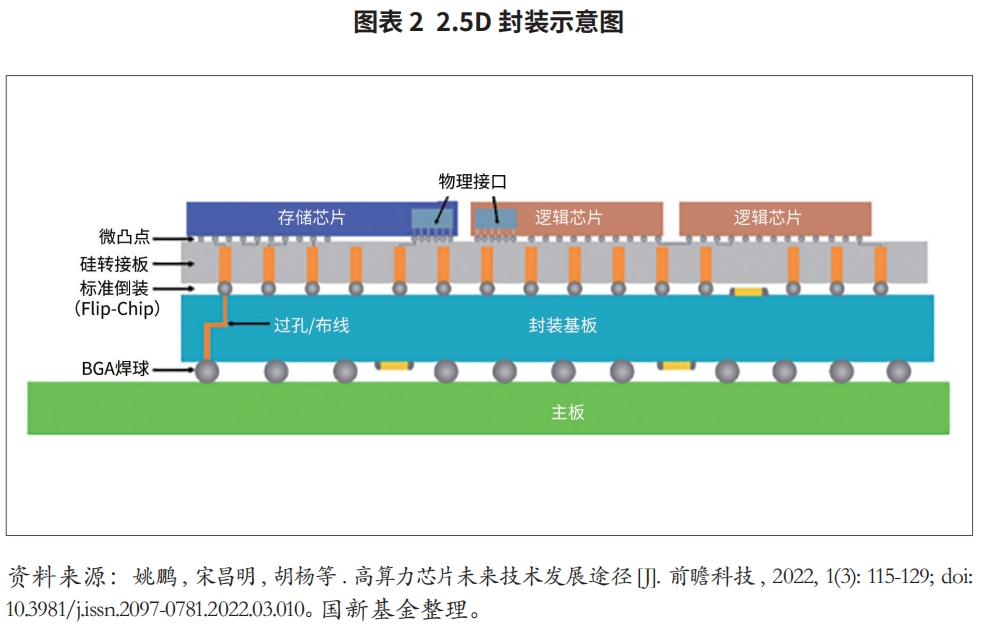

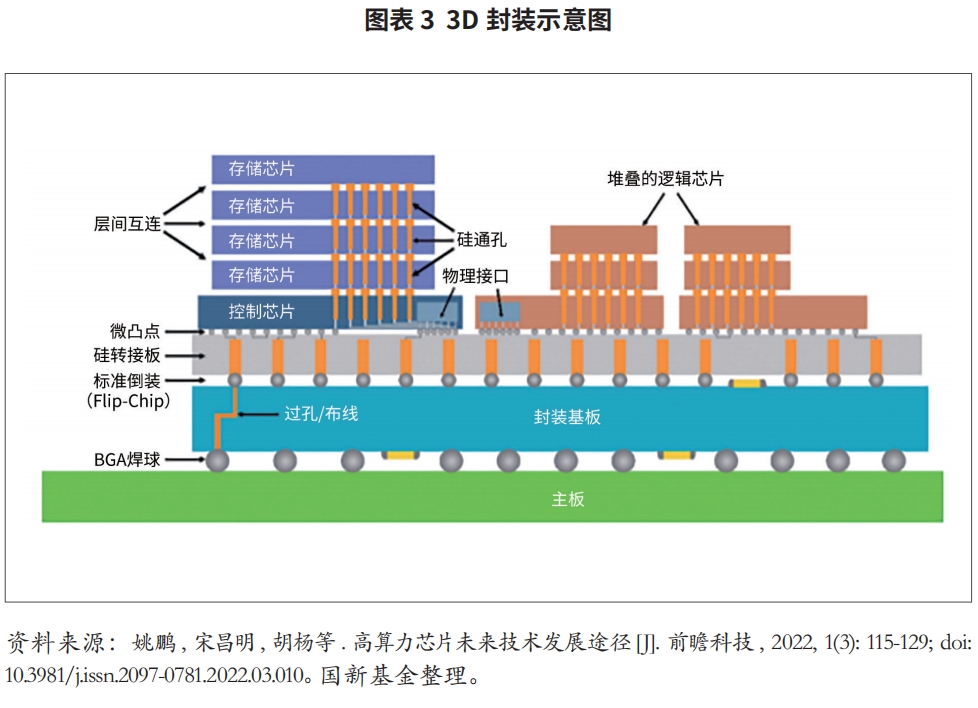

芯粒封装技术中,按照封装结构可分为2d、2.5d和3d。传统的2d封装成本低,但互连线的密度不高。2.5d封装通过硅转接板实现多颗芯片的互连和集成,使计算和存储靠的更近,提升芯片效能。目前2.5d封装已经大规模量产,台积电的cowos(chip on wafer on substrate)技术是典型代表。3d封装是将2颗或多颗芯粒通过硅通孔(through silicon via,tsv)、以面对背(face-to-back)的形式,或通过微凸点(micro-bumping)或混合键合(hybrid bonding)技术、以面对面 (face-to-face)的形式,在垂直方向直接堆叠,实现芯粒间和对外界的信号连接的技术。3d封装互连密度更高、距离更短、速度更快,使芯片的带宽提升、功耗下降,但门槛也较高,目前仅应用在cis(cmos图像传感器)、hbm dram、 3d nand、矿机芯片等硬件上,尚未大面积推广。此外,3d封装成本更高,还存在散热和应力问题。

(二)存算一体

存算一体又称存内计算(computing-in-memory,cim),指在存储器中进行计算和数据存储,可进一步实现计算和存储的器件级融合,存储单元同时也是执行单元,可显著降低功耗和减少延时,消除“存储墙”瓶颈。

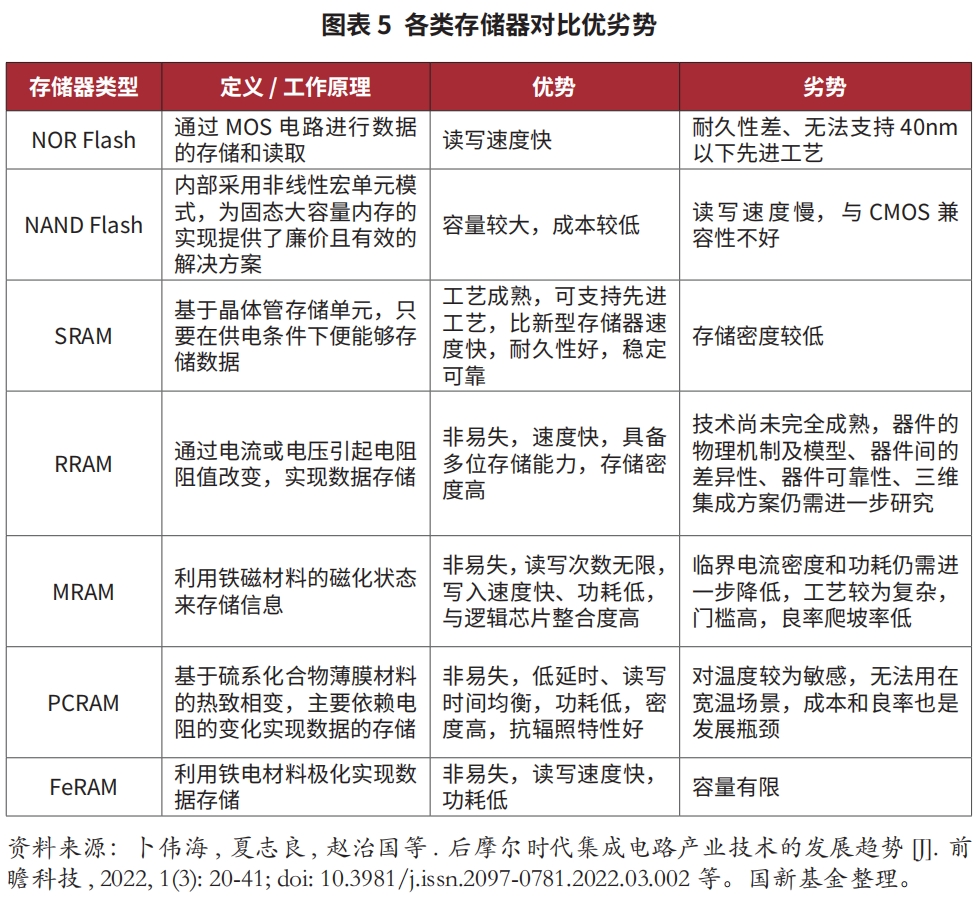

存算一体技术路线众多,从存储介质来看,底层器件主要分为两类,一类是相对更成熟的存储器,包括非易失性存储器(nvm)、静态随机存取存储器(sram)等,nvm中nor flash又更为成熟,但存在耐久性差、无法支持先进工艺的问题。为解决40nm以下节点先进工艺的替代性问题,出现了第二类新型存储器,包括阻变式随机存取存储器(rram)、磁性随机存取存储器(mram)、相变随机存取存储器(pcram)、铁电随机存取存储器(feram)等。

新型存储器虽然存储密度较高,但均无法解决耐久性、一致性问题,仍不够成熟。从设计芯片的角度看,sram路线较适合做存算一体,可以结合先进封装工艺弥补存储密度较低的劣势。 各类存储器具体优劣势如图表5所示。

除存储介质外,选择数字计算或模拟计算也是影响存算一体芯片性能的核心因素。数字存算一体架构在存储器内实现纯数字逻辑,可避免模拟计算导致的计算误差,同时激活全部存储器阵列,具有更高的能量效率和面积效率,还可借助eda工具大规模扩展。模拟计算能效优于数字计算,但易受干扰,精度较低,不适合大规模量产,目前主要用在信号链、电源、通讯领域。长期来看,模拟计算具有更广阔的前景,但20年内数字计算依然是主流。

综合来看,如果未来短期内新型存储器能够解决耐久性、一致性问题,以及与cmos的兼容性问题,将有较大发展潜力。否则中短期看,基于sram的数字存算一体芯片最有可能率先实现大规模商业化落地。另外值得注意的是,目前存算一体芯片更适用于小算力场景,为满足云端大算力需求,需要结合3d封装技术,以同时解决计算和数据存储容量的问题。

(三)类脑芯片

类脑芯片通过数学建模模拟人类大脑神经元在处理信息时的动力学特征,在芯片架构上不断接近人脑,在功耗和计算学习能力上超越传统芯片,其基础技术逻辑是实现脉冲神经网络(snn)算法。目前snn算法有较多不同的理论和模型,按照神经元编码方式主要分为两类:一类是按照脉冲的信息发放率,即基于时间变化的脉冲数量的平均值,对脉冲序列进行编码;另一类是按照脉冲时间间隔编码,如lif(leaky integrate fire)模型,即对输入脉冲在时间上求积分,超过阈值vthresh时输出一个脉冲,然后进入不应期。从长远角度看,类脑芯片是发展趋势,因为其更像人类的大脑,效率更高、功耗更低,但目前类脑芯片精度差且功能弱,从机理、算法到底层电路都仍处于探索阶段,整个产业链和生态尚不完善。

(国新基金)

注释

〔1〕 深度学习算法由一个个计算单元组成,这些计算单元即为算子(operator)。

〔2〕 姚鹏, 宋昌明, 胡杨等. 高算力芯片未来技术发展途径[j]. 前瞻科技, 2022, 1(3): 115-129; doi: 10.3981/j.issn.2097-0781.2022.03.010

免责声明

本文的分析及建议所依据的信息均来源于公开资料,我们对这些信息的准确性和完整性不作任何保证,也不保证所依据的信息和建议不会发生任何变化。我们已力求文章内容的客观、公正,但文中的观点、结论和建议仅供参考,不构成任何投资建议。投资者依据文章提供的信息进行投资所造成的一切后果,概不负责。文章未经书面许可,任何机构和个人不得以任何形式翻版、复制和发布。如引用、刊发,需注明出处为国新资讯,且不得对文章进行有悖原意的引用、删节和修改。

- 人工智能在投资领域应用及启示2023-11-06

- 长期资本管理公司破产的几点启示2023-10-13

- 储能产业发展趋势及投资机遇2023-10-13